Wybór generatora sygnału zegarowego do aplikacji

Konstruktor budujący urządzenie z układami cyfrowymi często staje przed dylematem wyboru odpowiedniego generatora sygnału zegarowego (taktującego). W praktyce można skorzystać z wielu rozwiązań, począwszy od generatorów RC wbudowanych w struktury układów, poprzez moduły generatorów o częstotliwości stałej lub przestrajanej napięciem oraz inne, specjalistyczne rozwiązania jak np. generator rubidowy. Duży wybór rozwiązań może przyprawić o zawrót głowy – który generator wybrać do swojej aplikacji i jakimi kryteriami kierować się?

Nie można użyć tego samego kryterium dobierając źródło sygnału zegarowego do różnych urządzeń. Wybór właściwego generatora jest zależny od szeregu czynników, np. od tego czy jego sygnał musi być synchronizowany z zewnętrznym sygnałem odniesienia, architektury mikroprocesora lub układu FPGA, rodzaju zastosowanych interfejsów, wymagań odnośnie do stabilności częstotliwości oraz jittera i innych. Istnieją aplikacje, w których krytyczne znaczenie mają niski jitter oraz małe zniekształcenia fazowe, ponieważ mają one bezpośredni wpływ na stopę błędów w szybkiej transmisji danych lub stosunek sygnał/szum podczas konwersji analogowo – cyfrowej.

Projektowanie urządzeń przeznaczonych do pracy w sieci, bezprzewodowej transmisji danych, transmisji sygnału wizji oraz przyrządów pomiarowych i testujących, staje się coraz bardziej złożone. Nie chodzi tu o sam hardware (chociaż i on musi podołać rosnącym wymaganiom), ale także o to, że inżynier musi dysponować odpowiednią wiedzą na temat rosnącej liczby protokołów komunikacyjnych, standardów transmisji danych oraz parametrów technicznych transmisji, które mają ogromny wpływ na projektowane urządzenia. Dodatkowo, najnowsze urządzenia są przystosowywane do pracy z wykorzystaniem wielu standardów. Na przykład, współczesne węzły telekomunikacyjne wspierają nie tylko standardy SONET/SDH oraz Ethernet, ale również powinny być przystosowane do przenoszenia cyfrowego, strumieniowego sygnału wizji. Aktualnie montowane stacje bazowe telefonii komórkowej obsługują nie tylko telefonię, ale również sieci WiMax i LTE. Kolejne przykłady można mnożyć. Jest to powodem, dla którego producenci sprzętu skupiają się głównie na implementowaniu nowych funkcjonalności i nie chcą marnować czasu na rozwiązywanie problemów związanych z hardware. Do tego można dodać wszechobecny trend do obniżania kosztu gotowego wyrobu.

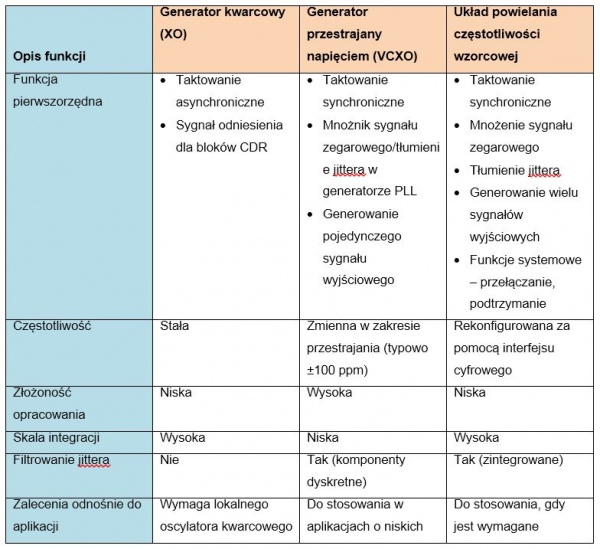

Wśród technik taktowania układów cyfrowych można wymienić trzy rodzaje: asynchroniczne (niezależnie od innych źródeł sygnału), synchroniczne (na podstawie sygnału wzorcowego – synchronicznie z innym źródłem) oraz przez powielanie częstotliwości wzorcowej.

Taktowanie asynchroniczne

Najczęściej stosowanym w technice cyfrowej i jednocześnie najprostszym źródłem sygnału zegarowego jest generator RC lub kwarcowy (XO) generujące sygnał o stałej częstotliwości, przeznaczony najczęściej dla pojedynczego komponentu – mikrokontrolera, układu FPGA itp. Generatory RC są bardzo wrażliwe na zmiany temperatury oraz zmiany parametrów komponentów ustalających częstotliwość i dlatego raczej nie nadają się do aplikacji wymagających dokładnego odmierzania czasu, np. do sterowania pracą UART. Ze względu na bardzo niski koszt implementacji są one jednak bardzo chętnie stosowane w niewymagających urządzeniach – zabawkach, timerach odmierzających czas z kilkuprocentową dokładnością, urządzeniach pracujących niezależnie od innych lub wykorzystujących do transmisji autonomiczne moduły itd.

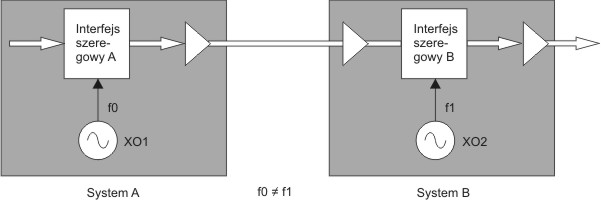

Generatory kwarcowe charakteryzują się znacznie lepszą stabilnością i są często wykorzystywane w aplikacjach pracujących asynchronicznie. Przykład systemu asynchronicznego pokazano na rysunku 1. Każdy z oscylatorów dostarcza lokalny sygnał odniesienia dla dwóch niezależnych domen sygnałów zegarowych. Oba systemy mogą być taktowane sygnałami o częstotliwości, która nie musi być identyczna. Wystarczającą dokładność zapewniają generatory kwarcowe lub krzemowe, ale w większości wypadków nie da się zastosować generatora RC chyba, że zostanie wprowadzona odrębna metoda synchronizacji transmisji szeregowej (np. kodowanie Manchester). W innym wypadku, np. przesyłając dane za pomocą UART jest wymagane, aby prędkości transmisji były identyczne z tolerancją co najwyżej 2%. W praktyce, nieskomplikowany generator kwarcowy umożliwia uzyskanie dokładności generowanej częstotliwości rzędu 0,5%, co jest w zupełności wystarczające dla transmisji UART.

Rysunek 1. Schemat blokowy systemu przesyłającego dane asynchronicznie, jednokierunkowo

Architektura zaprezentowana na rys. 1 dobrze nadaje się dla aplikacji pracujących w trybie burst. Ciągła wymiana danych wymaga bitów synchronizujących, dokładnego odmierzania czasu oraz bufora kolejki FIFO, aby zabezpieczyć się przed błędami transmisji.

Przykładami urządzeń asynchronicznych jest sprzęt do przetwarzania sygnału wizji oraz wyposażenie sieci Ethernet. Wybór generatora dla takiej aplikacji powinien być podyktowany częstotliwością generowanego sygnału, stabilnością jego fazy oraz wymaganiami odnośnie do dryftu temperaturowego czy wynikającego ze starzenia się komponentów.

Taktowanie synchroniczne

Synchronizacja sygnałów zegarowych jest zwykle używana w aplikacjach, które wymagają ciągłej komunikacji. W takiej sytuacji muszą być zminimalizowane opóźnienia transmisji wynikające z czasu propagacji w sieci. Najlepiej, aby czas propagacji sieci miał zawsze zbliżoną wartość. Aby to osiągnąć, aplikacje (włączając w to SONET/SDH, SyncE – Synchronous Ethernet, bezprzewodową retransmisję sygnału oraz transport sygnału wizji i fonii wysokiej jakości) wymagają, aby nadajnik i odbiornik pracowały taktowane sygnałami o tej samej częstotliwości.

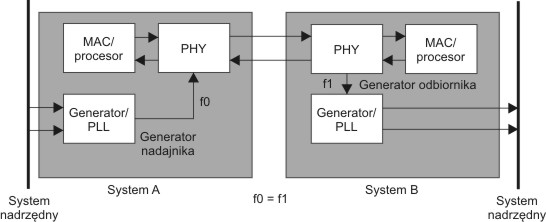

Przykład systemu pracującego synchronicznie pokazano na rysunku 2. Po stronie nadajnika, generator dostarcza sygnał taktujący transmisją o dużej prędkości. Pracuje on ze stałą częstotliwością, którą przyjmuje się jako sygnał zegarowy odniesienia. Zależnie od wymagań aplikacji, sygnał ten może być generowany lokalnie lub centralnie, np. może być pobierany z odbiornika GPS. Często w takiej sytuacji (przy sygnale odbieranym z zewnątrz) w urządzenie wbudowuje się generator PLL pełniący rolę regeneratora sygnału wzorcowego. Jego zadaniem jest wytwarzanie sygnału odniesienia, a przy tym tłumienie jittera, usunięcie niepożądanych zakłóceń oraz zapewnienie sygnału o niskim jitterze dla bloku PHY.

Rysunek 2. Schemat blokowy modułu do komunikacji synchronicznej, dwukierunkowej.

Po stronie odbiornika do odtworzenia sygnału zegara systemowego są używane bloki Clock oraz Data Recovery – CDR. Mogą one być wykonane z użyciem komponentów zewnętrznych lub zintegrowane wewnątrz PHY. Opcjonalnie, w celu umożliwienia blokom CDR szybkiego odbioru danych oraz do ustalenia częstotliwości sygnału zegarowego, jak również zapewniając rezerwę na wypadek awarii, można w odbiornik wbudować generator kwarcowy.

Odtworzony sygnał zegarowy przechodzi przez inny generator PLL obniżający (dzielący) jego częstotliwość. Lokalne funkcje pomiaru czasu mogą być zsynchronizowane z tym sygnałem lub z innym sygnałem lokalnym, który jest zsynchronizowany z centralnym źródłem głównego sygnału zegarowego. Synchronizacja ze źródłem zapewnia synchroniczną pracę generatorów sygnału zegarowego we wszystkich węzłach sieci. Generatory PLL używane w tej aplikacji mogą wymagać pętli fazowej o wąskim paśmie przenoszenia, aby odfiltrować niepożądany jitter.

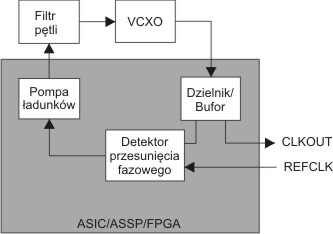

Generator PLL może być wykonany z elementów dyskretnych np. z użyciem specjalizowanego układu scalonego lub modułu generatora przestrajanego napięciem (VCXO), detektora fazy i filtra pętli. Zaleca się rozwiązanie wykorzystujące elementy dyskretne, gdy wymagania stawiane jitterowi oraz zniekształceniom fazowym są bardzo wysokie. W niektórych aplikacjach procesor lub układ FPGA mają zintegrowane detektor fazy oraz pompę ładunków, więc wymagane jest użycie jedynie generatora VCXO oraz zewnętrznego filtra pętli (rysunek 3). Pomimo tego rozwiązanie dyskretne ma wiele wad.

Wykonanie dyskretnej pętli PLL wymaga wiedzy i znajomości tematu, natomiast generator jest czuły na zaburzenia występujące na płytce drukowanej. Dodatkowo, dyskretny generator PLL zwykle dostarcza pojedynczego sygnału. Jeśli wymagania odnośnie do częstotliwości zegarowej zmienią się, to należy użyć innego generatora VCXO. W niektórych aplikacjach jest wymagane użycie kilku VCXO w celu wygenerowania wszystkich sygnałów zegarowych niezbędnych dla danej aplikacji. Co oczywiste – podwyższa to koszt rozwiązania. Aby sprostać takim potrzebom są produkowane układy scalone (np. Silicon Lab Si571), które eliminują konieczność stosowania wielu generatorów zegarowych i obniżają całkowitą cenę rozwiązania.

Rysunek 3. Schemat blokowy generator z zewnętrznym filtrem i generatorem VCXO przestrajanym napięciem

Powielanie częstotliwości wzorcowej

Często stosowaną metodą generowania sygnału zegarowego jest powielanie częstotliwości wzorcowej. Mimo iż określenie „układ mnożący” najczęściej odnosi się do komponentów analogowych mnożących sygnały lub prądy wejściowe, to dla potrzeb tego akapitu przyjmujmy, że określenie „mnożący” będzie w nim odnosiło się do układów powielających – mnożących częstotliwość wzorcową przez pewną stałą wartość.

Dla wytłumienia jittera zegarowego sygnału odniesienia w układzie mnożącym jest używane rozwiązanie wykorzystujące generator PLL, najczęściej zintegrowany w układzie scalonym. Układ mnożący utrzymuje stałą częstotliwość sygnału wyjściowego, filtruje niepożądany jitter i generuje sygnał o częstotliwości wynikającej z przemnożenia wejściowego sygnału odniesienia przez stałą wartość. Budując ten rodzaj generatora trzeba zwrócić szczególną uwagę na wybór układu mnożącego, ponieważ układy scalone poszczególnych producentów nie są równoważne funkcjonalnie. Dla aplikacji szybkiej transmisji danych za pomocą interfejsu szeregowego jest wymagane zastosowanie układów mnożących o najwyższej jakości, ponieważ tylko one są w stanie zapewnić niewielki jitter.

W danych katalogowych danego podzespołu powinno się odszukać informacje na temat maksymalnego i typowego jittera, a następnie porównać obie wartości. Układ mnożący, w którym wyspecyfikowano maksymalny jitter pozwala konstruktorowi na ustalenie budżetu jittera oraz określenie na tej podstawie parametrów czasowych układów w taki sposób, który zapewni wystarczający margines bezpieczeństwa w każdych warunkach transmisji. W kolejnym kroku warto zwrócić uwagę na pasmo przenoszenia układu mnożącego. Jeśli jest wymagane tłumienie jittera sygnału wzorcowego, to wówczas pasmo przenoszenia musi być mniejsze od 1 kHz. Na koniec należy potwierdzić, że układ mnożący może pracować w założonych przedziałach częstotliwości.

Zastosowanie wielowyjściowego układu mnożącego mającego możliwość ustalenia dla każdego z nich odrębnego mnożnika, pozwala na przełączanie się na różne częstotliwości sygnału zegarowego. W takiej sytuacji po przełączeniu nie traci się synchronizacji z sygnałem odniesienia, podczas gdy odbiornik może pracować szybciej np. kilkakrotnie próbkując sygnał wejściowy.

Układ mnożący w wypadku zaniku sygnału wzorcowego może przełączyć się na źródło alternatywne. Często buduje się aplikacje, w których jest monitorowana jakość wielu sygnałów wzorcowych i w wypadku wykrycia pogorszenia się parametrów lub wręcz przy zaniku sygnału głównego, generator przełącza się na alternatywne źródło odniesienia. Innym popularnym sposobem reagowania na zanik sygnału głównego jest podtrzymanie pracy generatora z częstotliwością sygnału, która występowała tuż przed zanikiem sygnału głównego.

W tabeli 1 umieszczono streszczenie wskazówek podanych w artykule. Upraszcza ona wybór właściwego źródła sygnału zegarowego dla projektowanego urządzenia. Tabela nie wyjaśnia czy należy użyć generatora kwarcowego czy krzemowego – przy wyborze rodzaju rozwiązania należy kierować się jego parametrami technicznymi, używając wskazówek zawartych w tabeli.

Jacek Bogusz,

j.bogusz@easy-soft.net.pl

Bibliografia:

- Silicon Laboratories: James Wilson „When to Use a Clock vs. an Oscillator”.

- Maxim Integrated: Tutorial 2141: "Determining Clock Accuracy Requirements for UART Communications", http://pdfserv.maximintegrated.com/en/an/AN2141.pdf.

Tabela 1. Tabela ułatwiająca wybór odpowiedniego sygnału zegarowego do aplikacji

Dodaj nowy komentarz