Translator poziomów napięć dla interfejsów SPI oraz I2C

Interfejsy szeregowe najczęściej używane są do komunikacji pomiędzy układami w obrębie urządzenia, modułu czy wręcz płytki drukowanej. Najczęściej stosowane i przez to najczęściej spotykane są interfejsy I2C oraz SPI. W dzisiejszych czasach konstruktor może napotkać jeden problem: często mikrokontrolery czy mikroprocesory zasilane są dużo niższym napięciem niż układy peryferyjne. Wykonywane są one w bardzo dużej skali integracji, w technologii, w której wymiary pojedynczego tranzystora to ułamki mikrometra. Takie układy zapewniają dużą wydajność (większy stopień upakowania elementów, krótsze połączenia pomiędzy elementami) ale wymagają do zasilania napięcia rzędu 1,5 V. Co zrobić, gdy pozostałe układy komunikujące się z procesorem zasilane są przez napięcie o innej wartości? Na przykład przetworniki analogowo – cyfrowe, które dla uzyskania dobrej dynamiki potrzebują napięć zasilania 5 V i wyższych? Konieczna staje się wówczas budowa tzw. translatora poziomów napięć. Dalej zostanie omówiony przykład takiej aplikacji dostosowany do pracy z interfejsami szeregowymi.

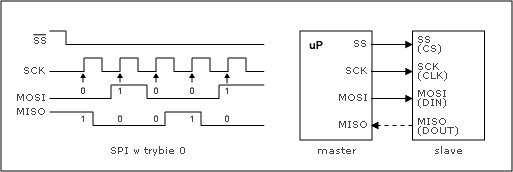

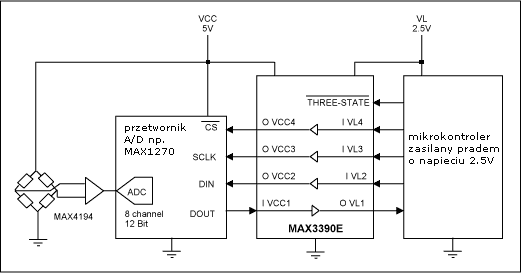

Interfejs SPI najczęściej używa 3, rzadziej 2 czy 4 sygnałów. W tych rozważaniach musimy uwzględnić warunki ekstremalne, to znaczy wykorzystanie wszystkich 4 sygnałów: MISO (wejście układu Master), MOSI (wyjście układu Master), SCK (sygnał zegarowy) i SS (wybór układu Slave). Kilka urządzeń może być podłączonych do tych samych linii transmisyjnych. Wspólne są dla nich linie MISO, MOSI, SCK. Wybór układu obywa się przez oddzielną linię SS. Niektóre układy z interfejsem SPI można łączyć w kaskady wykorzystując do tego celu dedykowane wejścia / wyjścia danych. Transmisja odbywa się synchronicznie, z prędkością do 2Mbit aczkolwiek zdarzają się wykonania interfejsów o większej szybkości. W przypadku gdy układ Master tylko wysyła dane, można zrezygnować z podłączenia linii MISO, co zaznaczono na rysunku 1 w postaci linii przerywanej.

Rysunek 1. Interfejs SPI

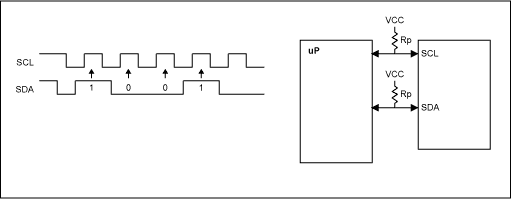

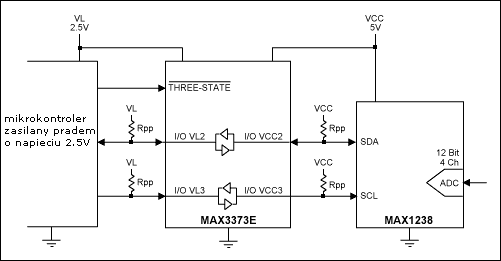

Standard I2C definiuje dwie dwukierunkowe linie transmisyjne: SDA i SCL. Tej pierwszej układy używają do przesyłania danych oraz potwierdzenia ich odbioru czy też zgłoszenia się po poprawnym zaadresowaniu. Ta druga wykorzystywana jest jako zegar transmisji i w niektórych przypadkach do jej opóźnienia (spowolnienia) i arbitrażu. Każde urządzenie posiada unikalny, 7- lub 10-bitowy adres. Dane przesyłane są typowo z prędkością do 100 kbit/s, rzadziej 400 kbit/s. Zdarzają się również rozwiązania przesyłające dane z szybkością do 3,4 Mbit/s. I2C wymaga zastosowania rezystorów pull-up, których wartości dobiera się w zależności od wymaganych parametrów transmisji oraz ilości dołączonych układów i rodzaju (także długości) połączenia pomiędzy nimi. Jak łatwo się zorientować, są to czynniki tworzące pojemność linii magistrali transmisyjnej.

Rysunek 2. Interfejs I2C

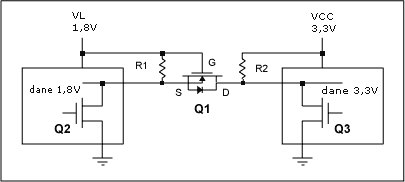

Na rysunku 3 przedstawiono prosty translator poziomów wykonany w oparciu o tranzystor MOS. Kilka słów na temat zasady działania. Jeśli żaden z tranzystorów wyjściowych Q2 i Q3 nie jest otwarty, to napięcie UGS pomiędzy źródłem (S) i bramką (G) tranzystora Q1 wynosi 0V, napięcie US pomiędzy masą a jego źródłem 1,8 V a napięcie UD pomiędzy drenem a masą 3,3 V. Jeśli Q2 zostanie otwarty, napięcie UGS wzrośnie do 1,8 V i spowoduje otwarcie tranzystora Q1. Poprzez złącza dren – źródło Q1 i Q2 popłynie prąd wymuszając stan niski na doprowadzeniu „dane 3,3 V”. Jeśli napięcie na wyprowadzeniu Q3 pojawi się stan niski, to dioda dołączona na zewnątrz bądź znajdująca się w strukturze tranzystora zacznie przewodzić, wymuszając stan niski na doprowadzeniu źródła (S) tranzystora Q1. Napięcie UGS przyłożone do bramki Q1 wzrośnie do około 1,5 V (VL – napięcie na diodzie) i tranzystor zacznie przewodzić prąd, powodując stan niski do doprowadzeniu portu „dane 1,8 V”. Jest to prosty, dwukierunkowy translator napięć logicznych.

Rysunek 3. Translator poziomów napięć 1,8 V -> 3,3 V wykonany z użyciem tranzystora MOS.

W analizie pominąłem jeden ważny fakt – nie ma tranzystorów idealnych i w związku z tym rezystancja pomiędzy drenem a źródłem nigdy nie będzie wynosić 0Ω. W praktyce waha się pomiędzy 20 a 130 Ω i zależy od płynącego przez złącze prądu. Tak więc w najgorszym przypadku na tranzystorze może się odłożyć spadek napięcia: dla portu zgodnego z I2C przy prądzie rzędu 3 mA będzie to około 0,4 V a dla bufora 74LVC125 przy prądzie 24 mA około 0,55 V. W takim przypadku napięcie UGS nie będzie już 1,8 V ale niższe, zależne od użytego rezystora R1 i rezystancji przewodzenia dren – źródło tranzystora Q1. Pojawia się kilka kwestii do rozważenia w związku z rzeczywistymi parametrami tranzystora:

- Przy napięciu VL o wartości 1,8 V lub mniejszej, wybór tranzystorów MOSFET o wystarczająco niskim progu napięcia bramka - źródło jest raczej ograniczony. Jednym z kandydatów może być TN2501 firmy Supertex.

- Czas narostu / opadania zboczy sygnałów zależny jest od wartości rezystancji R1 i R2 i liczby urządzeń dołączonych do linii interfejsu (czyli pośrednio od pojemności połączeń). Pojemność montażowa jest bowiem ładowana napięciem zasilającym poprzez rezystory pull-up. Tak więc właściwy dobór rezystancji R1 i R2 bardzo wpływa na osiągane szybkości transmisji danych według prostej zależności: im mniejsza rezystancja, tym krótsze czasy narostów a co za tym idzie - osiągane są większe szybkości transmisji. Niestety wzrasta również pobór prądu a nie jest to zjawisko zbyt korzystne zwłaszcza w układach zasilanych z baterii.

- Za pomocą tego prostego obwodu nie jest możliwa praca trójstanowa i odłączenie R1/R2. Tak więc nie ma możliwości odłączania układów od linii interfejsu i praca tylko i wyłącznie z układami zaadresowanymi. Brak jest możliwości budowy gałęzi układów o tych samych adresach.

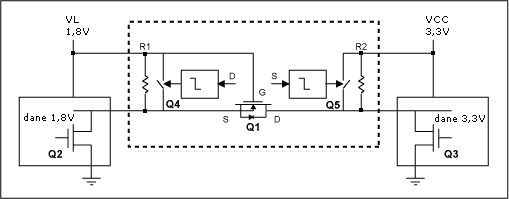

Oczywiście wyżej opisywane rozwiązanie jest proste i tanie w zastosowaniu. Może być z powodzeniem używane w mniej wymagających aplikacjach. Ale dla tych bardziej zaawansowanych, o większych prędkościach przesyłu, nie nadaje się. Czy można sobie poradzić w takie sytuacji? Pewne rozwiązanie podsuwa firma MAXIM-DALLAS. Zostało ono użyte w strukturze układów z rodziny MAX3372E..3393E. Jego uproszczony schemat został przedstawiony na rysunku 4 i polega na użyciu aktywnego rezystora pull-up.

Rysunek 4. Zasada działania układów z rodziny MAX3372E..3393E

W strukturze układu dodano dwa nowe tranzystory CMOS oznaczone na rysunku 4 jako Q4 i Q5. Narastające zbocze sygnału powoduje krótkie zwarcie drenu ze źródłem znacznie skracając czas narostu sygnału a tym samym przyspieszając transmisję danych. Minimalna gwarantowana przez producenta wartość prędkości transmisji to 8Mbit a jeśli różnica pomiędzy VCC i VL jest mniejsza niż 0,8V, to można osiągnąć nawet i 16Mbit! Dodatkowo wprowadzono możliwość pracy trójstanowej i odłączania rezystorów pull-up. Dzięki temu układ doskonale nadaje się do budowy wielopunktowej (wieloukładowej) sieci układów z interfejsem I2C o tym samym adresie. Można je bowiem galwanicznie od siebie separować. Dodatkowymi atutami mogą być zabezpieczenie przed wyładowaniami elektrostatycznymi do 15kV oraz zabezpieczenie termiczne. Typowe aplikacje – zastosowania do wykorzystania przy budowie interfejsu SPI oraz I2C przedstawiono na rysunkach 5 i 6.

Rysunek 5. Wykorzystanie układu MAX3390E do translacji poziomów napięć interfejsu SPI.

Rysunek 6. Wykorzystanie układu MAX3390E do translacji poziomów napięć interfejsu I2C.

Zależnie od liczby układów dołączonych do magistrali transmisyjnych, może być wymagane opcjonalne użycie rezystorów pull-up. Układy MAX mają wewnątrz struktury rezystory o wartości 10 kΩ. Jest to wartość zupełnie wystarczająca dla pojemności linii transmisyjnych nieprzekraczającej 90 pF. Przy większych pojemnościach połączeń należy na podstawie noty aplikacyjnej dobrać właściwą wartość rezystora pull-up.

Jacek Bogusz

j.bogusz@easy-soft.net.pl

Odpowiedzi

Fajnie, przystępnie

Fajnie, przystępnie wytłumaczone. Dziękuję i pozdrawiam!

dziękuje

dziękuje ten artykuł bardzo mi pomógł :)

Dodaj nowy komentarz